# ISPSD References Kumamoto

37th International Symposium on Power Semiconductor Devices and ICs

Sponsored by

This conference is supported by JSPS KAKENHI Grant Number 24HP0701.

This conference is supported by International Exchange Program of National Institute of Information and Communications Technology (NICT)

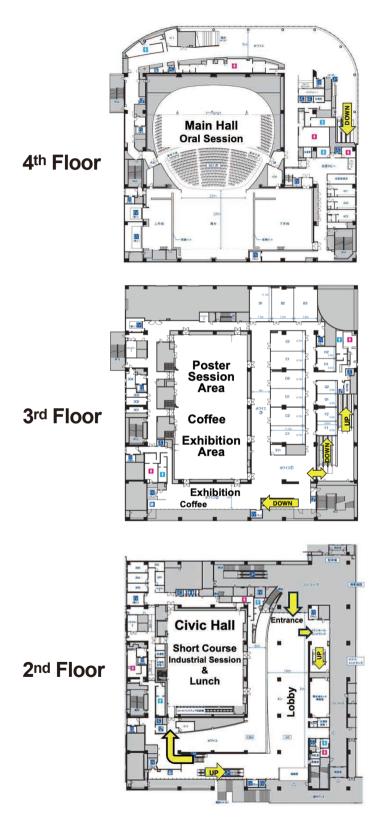

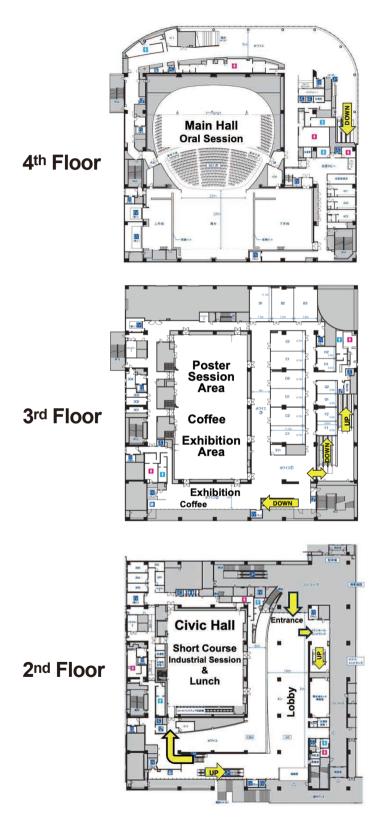

#### KUMAMOTO-JO (CASTLE) HALL FLOOR DIRECTRY

# SCHEDULE AT A GLANCE

| Time  | June 1 Sun                          | June 2 Mon                      | June 3 Tue              | June 4 Wed                                           | June 5 Thu              |

|-------|-------------------------------------|---------------------------------|-------------------------|------------------------------------------------------|-------------------------|

| 8:30  | Short Course Opening<br>8:40 - 9:30 | 8:30 - 9:00<br>Opening Session  | 8:40 - 10:20            | 8:40 - 10:20                                         | 8:40 - 10:20            |

| 9:00  | Short Course 1                      |                                 | 8:40 - 10:20            | SiC-4                                                | 8:40 - 10:20<br>HV-2    |

| 9:30  | 9:30 - 10:20                        | 9:00 - 10:20                    | Low Voltage             | Gallium Oxide                                        | Multi-Gate Technology   |

| 10:00 | Short Course 2                      | Plenary Session                 | Power Devices           | and Diamond Devices                                  | and SJ Devices          |

| 10:30 | 10:20 - 10:50<br>Coffee             | 10:20 - 10:50<br>Coffee         | 10:20 - 10:50<br>Coffee | 10:20 - 10:50<br>Coffee                              | 10:20 - 10:50<br>Coffee |

| 11:00 | 10:50 - 11:40                       | 10:50 - 12:30                   |                         | 10:50 - 12:30                                        | 10:50 - 12:30           |

| 11:30 | Short Course 3                      | HV-1                            | 10:50 - 12:30           | SiC-2                                                | SiC-3                   |

|       | 11:40 - 12:30                       | New Power Device Designs        | Power IC Design         | Design Approaches and<br>Physics for Reliability and | Novel Devices           |

| 12:00 | Short Course 4                      | and Gate Control Method         | Tower to besign         | Performance of SiC Devices                           | and Ruggedness of SiC   |

| 12:30 |                                     |                                 |                         |                                                      |                         |

| 13:00 | 12:30 - 14:00                       | 12:30 - 14:00                   | 12:30 - 14:00           | 12:30 - 14:00                                        | 12:30 - 14:00           |

| 13:30 | Lunch                               | Lunch                           | Lunch                   | Lunch                                                | Lunch                   |

| 14:00 |                                     |                                 | 14:00 - 15:20           |                                                      | 14:00 - 15:20           |

|       | 14:00 - 14:50<br>Short Course 5     | 14:00 - 15:40<br><b>SiC-1</b>   | GaN-2                   | 14:00 - 15:40<br><b>PK</b>                           | GaN-3                   |

| 14:30 | 14:50 - 15:40                       | Performance of                  | GaN Power Device        | Packaging                                            | Novel GaN Power Device  |

| 15:00 | Short Course 6                      | Superjunction SiC devices       | Reliability and Tests   | Technologies                                         | and Technologies 2      |

| 15:30 |                                     | 15:40 - 16:10                   | Coffee                  | 15:40 - 16:00                                        | Closing Session         |

| 16:00 | 15:40 - 16:30<br>Short Course 7     | Coffee                          | 15:40 - 17:40           | Coffee                                               |                         |

| 16:30 | 16:30 - 17:00                       | 16:10 - 17:50                   | Poster Session 1        | 16:00 - 18:00                                        |                         |

| 17:00 | Coffee                              | GaN-1<br>Novel GaN Power Device | LVT/ICD/GaN             | Poster Session 2                                     |                         |

|       |                                     | and Technologies 1              |                         | HV/PK/SiC                                            |                         |

| 17:30 | 17:00 - 19:00<br>Industrial         |                                 |                         |                                                      |                         |

| 18:00 | Session                             |                                 |                         |                                                      |                         |

| 18:30 | Coston                              |                                 |                         |                                                      |                         |

| 19:00 |                                     | Welcome                         |                         |                                                      |                         |

| 19:30 |                                     | Reception                       | AdCom Meeting           |                                                      | TPC Meeting             |

| 20:00 |                                     |                                 | (Invitation Only)       | Banquet                                              | (Invitation Only)       |

|       |                                     |                                 |                         | Hall of Fame                                         |                         |

| 20:30 |                                     |                                 |                         |                                                      |                         |

| 21:00 |                                     |                                 |                         |                                                      |                         |

# **Recording and Photography Policy**

IEEE policy prohibits video recording or photographing of presentations unless permission from the presenter is obtained in advance. Photographing of people or social events is permitted.

#### WiFi

DENSO is protecting the planet without sacrificing freedom of movement. By reducing environmental loads, making mobility more widely available, and improving energy efficiency, we can offset environmental impacts throughout society. Deeper connections between mobility and society will help protect the environment.

Together, we can manage energy usage more effectively on a global scale.

# Freedom of movement combined with environmental protection

Mobility Well-being

# Why SiC from Infineon?

COOLSICITY

Enhanced system longevity and performance – Above standard quality testing and best in class R<sub>DS(on)</sub>

Faster time-to-market and system support – 29 evaluation boards and reference designs

Accelerated design scalability – Comprehensive portfolio of 9 voltage classes, 7 discrete packages, 6 module housings, wide R<sub>DS(on)</sub> ranges

Learn more www.infineon.com/coolsic-g2

# Creating New Value for Mobility with Advanced Semiconductor Technology

MIRISE Technologies was established in April 2020 as a joint venture between DENSO and TOYOTA.

MIRISE focuses on three semiconductor technology areas for CASE.

# Better begins here.

Starting here and now, we want to make each new day better than before, spreading positivity and joy among people and uplifting society. At Mitsubishi Electric, our purpose goes beyond supporting your daily life. We are here to enrich it.

# TABLE OF CONTENTS

Schedule at a glance

| Recording and Photography Policy & Wi-Fi |    |

|------------------------------------------|----|

| Advertisements (Diamond Sponsors)        |    |

|                                          |    |

| Message from the Chair ······            | 2  |

| Organization ·····                       | 3  |

| Organizing Committee                     | 3  |

| Advisory Committee                       | 3  |

| Technical Program Committee              | 4  |

| General Information ······               | 6  |

| Presenter Instructions                   | 8  |

| Social Events ·····                      | 9  |

| Lunch ·····                              | 9  |

| Awards                                   | 10 |

| ISPSD Hall of Fame                       | 15 |

| Plenary Talks                            | 17 |

| Short Course ·····                       | 18 |

| 5                                        | 20 |

| Sponsors ·····                           | 52 |

| Exhibitors / Other Sponsors              | 54 |

| Exhibition Floor Map                     | 55 |

| Industrial Session                       | 56 |

| ISPSD 2026 Call for Papers ·····         | 57 |

| Advertisements $\cdots$ 59 $\sim$        | 63 |

#### **MESSAGE FROM THE CHAIR**

As the General Chair of ISPSD, I sincerely hope that all participants will enjoy this conference as a special and inspiring time. ISPSD is not only a technical conference, but also a place where people from different countries, regions, companies, and universities can come together to freely discuss and share their experiences. I believe that the true value of ISPSD lies in this open and friendly atmosphere, where mutual understanding can grow. I hope this conference will be a meaningful and memorable experience for every power semiconductor specialist.

This kind of ISPSD has been made possible thanks to the continuous efforts of many people who supported past conferences—especially the former General Chairs, Technical Program Chairs, organizing committee members, and sponsors. Before ISPSD was established around 1990, the field of power semiconductor device technology was not clearly defined. It was often considered part of the broader semiconductor field, including LSI, or as a component of power electronics. The pioneers who founded ISPSD made great efforts to create an international conference focused on power semiconductor device technology—and they succeeded in establishing a new and distinct technical field, as well as the ISPSD community. I would like to express my deep appreciation to all those who contributed to past ISPSDs.

New challenges are also important for ISPSD to maintain and grow the community. One such challenge this year is the introduction of the full paper submission scheme. This change was made to improve the quality of the review process and to shorten the time from submission to presentation. I understand that this required significant effort from the Technical Program Committee, and I would like to express my sincere thanks to all the committee members for their great efforts.

I would also like to mention the Short Course. This year, we invited lecturers from various countries and regions to give compact and informative talks on advanced technologies related to power semiconductors. I hope many of you will join and enjoy the course.

Another highlight of this year's ISPSD is the strong connection with industry. We have 30 company exhibition booths, along with an Industry Session where companies will introduce their latest technologies.

This year, ISPSD is fully sponsored by the Institute of Electrical Engineers of Japan (IEEJ), with technical co-sponsorship from IEEE EDS, PELS, and IAS. We also received strong support from Kakenhi and NICT grants, and many companies kindly supported us as sponsors. I am very thankful for their contributions.

Welcome to ISPSD 2025 in Kumamoto and enjoy the conference!

Ichiro Omura General Chair, ISPSD 2025

#### ORGANIZATION

#### **ORGANIZING COMMITTEE**

**General Chair** Ichiro Omura, Kyushu Institute of Technology, Japan **Technical Program Committee Chair** Yuichi Onozawa, Fuii Electric, Japan **Past General Chair** Nando Kaminski, University of Bremen, Germany **Vice General Chair** David Sheridan, Alpha & Omega Semiconductor, USA **Past Technical Program Committee Chairs** Tom Chun-Lin Tsai, TSMC, Taiwan Ulrike Grossner, ETH Zurich, Switzerland **Vice Technical Program Committee Chair** Sameh Khalil, Infineon Technologies, USA **Short Course Chair** Tatsuya Nishiwaki, Toshiba Electronic Devices & Storage, Japan **Sponsorship and Exhibition Chair** Naruhisa Miura, Mitsubishi Electric, Japan **Publication Chair** Yujiro Takeuchi, Hitachi, Japan **Social Event Chair** Masakiyo Sumitomo, Denso, Japan Treasurer

Kota Ohi, Fuji Electric, Japan

#### **ADVISORY COMMITTEE**

Gehan Amaratunga, Cambridge University, UK Kevin Chen, Hong Kong University of Science and Technology, Hong Kong, China Tat-Sing Paul Chow, Rensselaer Polytechnic Institute, USA Mohamed Darwish, MaxPower Semiconductor, USA Don Disney, Infineon Technologies, Germany Oliver Häberlen, Infineon Technologies, Austria Kimimori Hamada, Huawei Technologies, Japan Nando Kaminski, Bremen University, Germany Dan Kinzer, Navitas Semiconductor, USA Leo Lorenz, ECPE, Germany Gourab Majumdar, Mitsubishi Electric, Japan Peter Moens, onsemi, Belgium Mutsuhiro Mori, Waseda University, Japan Wai Tung Ng, University of Toronto, Canada Hiromichi Ohashi, NPERC-J, Japan Yasukazu Seki, Fuji Electric, Japan John Shen, Simon Fraser University, Canada Kuang Sheng, Zhejiang University, China M. Ayman Shibib, Vishay Siliconix, USA Johnny Sin, JSAB Technologies Limited, Hong Kong, China Jan Šonský, InnoScience, Belgium Yoshitaka Sugawara, SiC Power Electronics Network (SPEN), Japan Richard K. Williams, Adventive Technology, USA

#### **TECHNICAL PROGRAM COMMITTEE**

#### **Technical Program Committee Chair**

Yuichi Onozawa, Fuji Electric, Japan

#### **High Voltage Devices (HV)**

#### **Category Chair**

Ayanori Gatto, Mitsubishi Electric, Japan

#### **Members**

Karthik Padmanabhan, Alpha and Omega Semiconductor, USA Umamaheswara Reddy Vemulapati, Hitachi Energy, Switzerland Yusuke Yamashita, Toyota Central R&D Labs, Japan Wentao Yang, Huawei Technologies, China Tanya Trajković, Camutronics, UK Craig Fisher, Vishay, UK Ming Qiao, University of Electronic Science and Technology of China, China Kota Ohi, Fuji Electric, Japan

#### Low Voltage Devices and Power IC Device Technology (LVT)

#### **Category Chair**

Atsushi Sakai, Renesas Electronics, Japan

#### Members

Tatsuya Nishiwaki, Toshiba Electronic Devices & Storage, Japan Raffaella Roggero, STMicroelectronics, Italy Jaehyun Yoo, Samsung Electronics, Korea Steven Thomas Peake, Nexperia, UK KwangYoung Ko, DB HiTek, Korea Tanuj Saxena, onsemi, USA Kuo-Ming Wu, TSMC, Taiwan Xin Lin, NXP Semiconductors, USA

#### **Power IC Design (ICD)**

#### **Category Chair**

Makoto Takamiya, The University of Tokyo, Japan

#### Members

Jingshu Yu, Intel, USA Bruno Allard, INSA Lyon, Ampère-lab, France Christophe Tourniol, STMicroelectronics, France Siyang Liu, Southeast University, China Wei-Jia Zhang, Analog Device, USA Karthik Jayaraman, Renesas Electronics, USA Leon Wang, Omnivision Semiconductor, China

#### GaN and Nitride-based Compound Materials: Device and Technology (GaN)

#### **Category Chair**

Yasuhiro Uemoto, Infineon Technologies, Japan

#### **Members**

Lan Wei, University of Waterloo, Canada Oliver Hilt, Ferdinand-Braun-Institut, Berlin, Germany Akira Nakajima, AIST, Japan Hiroyuki Handa, Panasonic Holdings, Japan Benoit Bakeroot, IMEC and Ghent University, Belgium Tom Chun-Lin Tsai, TSMC, Taiwan Dong Seup Lee, Texas Instruments, USA Grace Xing, Cornell University, USA Na Ren, Zhejiang University, China Roy K.-Y. Wong, National Tsing Hua University, Taiwan Hong Zhou, Xidian University, China

#### SiC and Other Materials: Device and Technology (SiC)

#### **Category Chair**

Hiroshi Kono, Toshiba Electronic Devices & Storage, Japan

#### Members

Jeff Joohyung Kim, Wolfspeed, USA Song Bai, Nanjing Electronic Device Institute, China Alexander Bolotnikov, onsemi, USA Ulrike Grossner, ETH Zurich, Switzerland Takaaki Tominaga, Mitsubishi Electric, Japan Rudolf Elpelt, Infineon Technologies AG, Germany Peter Losee, Qorvo, USA Woongje Sung, University at Albany, USA Noriyuki Iwamuro, University of Tsukuba, Japan Shinsuke Harada, AIST, Japan Kung-Yen Lee, National Taiwan University, Taiwan Michele Riccio, University of Naples Federico II, Italy Cheng-Tyng Yen, Fast SiC Semiconductor, Taiwan

#### Module and Packaging Technologies: System Integration in Package (PK)

#### **Category Chair**

Haruka Shimizu, Hitachi, Japan

#### Members

Wei-Chung Lo, Industrial Technology Research Institute, Taiwan Xavier Jorda, IMB-CNM, Spain Emre Gurpinar, Sikorsky Aircraft, USA Chris Bailey, Arizona State University, USA Makoto Shibuya, Texas Instruments, Japan Stefan Oehling, Semikron-Danfoss, Germany Elena Mengotti, ABB Research Center, Switzerland

# **GENERAL INFORMATION**

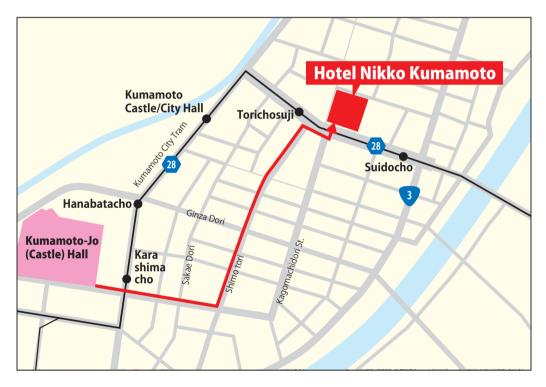

#### **Conference Venue**

Kumamoto-Jo (Castle) Hall 3-40, Sakuramachi, Chuo-ku, Kumamoto-city, Kumamoto, 860-0805 TEL: +81-96-312-3737 FAX: +81-96-312-3738

#### Registration

In order to participate in the ISPSD 2025 conference, you must register online for the conference at www.ispsd2025.com using your credit card.

#### **Registration Fees – Symposium**

|                           | Early registration<br>until April 9, 2025 23:59 JST | Regular registration<br>from April 10, 2025 |

|---------------------------|-----------------------------------------------------|---------------------------------------------|

| IEEE/IEEJ Member          | 100,000 JPY                                         | 110,000 JPY                                 |

| Non-member                | 110,000 JPY                                         | 120,000 JPY                                 |

| Student IEEE/IEEJ Member* | 60,000 JPY                                          | 65,000 JPY                                  |

| Student Non-member*       | 65,000 JPY                                          | 70,000 JPY                                  |

Additional tickets for banquet and welcome reception:

Welcome Reception: 5,000 JPY/ticket

Banquet: 20,000 JPY/ticket

Each participant can purchase up to two additional tickets for their accompanying persons.

#### **Registration Fees – Short Course**

|                           | Early registration until April<br>9, 2025 23:59 JST | Regular registration from<br>April 10, 2025 |

|---------------------------|-----------------------------------------------------|---------------------------------------------|

| IEEE/IEEJ Member          | 40,000 JPY                                          | 45,000 JPY                                  |

| Non-member                | 45,000 JPY                                          | 50,000 JPY                                  |

| Student IEEE/IEEJ Member* | 25,000 JPY                                          | 30,000 JPY                                  |

| Student Non-member*       | 30,000 JPY                                          | 35,000 JPY                                  |

Applicants must be full-time students at the time of the Conference and need to upload their valid student ID card scanned from both sides or another proof of full-time study.

Note: Payments must be received by the corresponding deadlines (early or regular), otherwise the subsequent rate will be automatically applied.

#### The registration fee includes:

Participant

Student

Session (June 2-5, 2025) Exhibition (June 2-5, 2025) Lunch/Coffee (June 2-5, 2025) Welcome Reception (June 2, 2025) Banquet (June 4, 2025) Proceedings (Online) Industrial Session (June 1, 2025) Session (June 2-5, 2025) Exhibition (June 2-5, 2025) Lunch/Coffee (June 2-5, 2025)

Welcome Reception (June 2, 2025)

Proceedings (Online) Banquet is not included and can be purchased separately (20,000 JPY) Industrial Session (June 1, 2025) Short Course (June 1, 2025) Short Course Attendance Short Course Printed Handout Coffee Breaks, Lunch Industrial Session

#### **Methods of Payment**

Registration fees must be paid in JPY: Credit Card Only

#### Receipt

Receipt will be available from the registrants' MyPage after 19 May, 2025

#### **Cancellations and Refunds**

The ISPSD 2025 Secretariat must be notified in writing by e-mail at ISPSD2025@c-linkage.co.jp in the conference of the cancellation of the registration. Cancellation by phone call will not be accepted. The appropriate refunds will be made after the conference.

The following cancellation conditions apply:

Cancellations received<br/>until April 9, 2025:Refund<br/>full refund of the registration feeApril 10 - 30, 2025:50 % of the registration feefrom 1 May 2025:no refundIn case of any change in registration, Convention Linkage, Inc. reserves the right to charge a 5,000 JPY<br/>handling fee.

In case of cancellation of the conference due to force majeure, Convention Linkage, Inc. reserves the right to charge a 5,000 JPY handling fee.

Name Change

No name change is accepted.

#### **Recording and Photography Policy**

IEEE policy prohibits video recording or photographing of presentations unless permission from the presenter is obtained in advance. Photographing of people or social events is permitted.

# **PRESENTER INSTRUCTIONS**

# **Instructions for Oral Speakers**

#### **Presentation time**

Oral papers presentation time is 15 minutes for presentation plus 5 minutes for Q&A, total 20 minutes. All speakers are strictly requested to keep the time of their presentation.

#### Venue

Main Hall on the 4th floor.

Presenters should be at the standby seat that will be located in the front row of the seats before their session start time.

#### How to prepare presentation slides

The presentation slides should be prepared in 16:9 format by Microsoft PowerPoint (2013 or higher) or PDF. Only fonts included in the basic installation of MS-Windows (English version) are available.

Recommended fonts are: Century, Century Gothic, Arial, Times New Roman, Tahoma, and Calibri. Do NOT use special characters.

Embedding pictures (GIF, PNG and BMP) or videos (WMV and MP4) into the slides is accepted, but do not increase the file size by unnecessarily high resolution material.

#### How to submit presentation slides at the conference

The presentation slides should be uploaded to an on-site PC from your USB stick and check properly working before start of the previous session at the latest.

(e.g. for a session starting at 10:50, it should be done by 8:40 at the latest)

Your own computer is NOT allowed for the presentation.

If you have any inconvenience with data transfer via USB stick, please contact the secretariat.

# **Instructions for Poster Presenters**

#### **Presentation time**

LVT/ICD/GaN category: 15:40 - 17:40 on Tuesday, June 3

HV/PK/SiC category: 16:00 - 18:00 on Wednesday, June 4

Poster presenters are requested to present in front of their poster and answer questions during the entire session time.

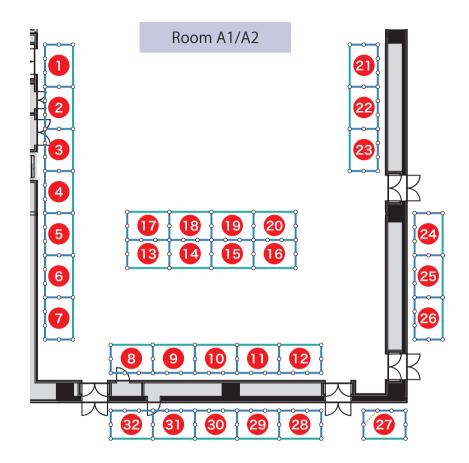

#### Venue

A3 and A4 Conference Room on the 3rd floor.

#### How to prepare a poster

The poster must be prepared in PORTRAIT style. The recommended dimensions are 84.1  $\times$  118.9 cm wide (format A0).

Do NOT exceed the overall dimensions of the poster board (210 cm high by 90 cm wide).

#### Set-up and Dismantling time

All posters are required to be displayed during the entire conference period from June 2 to 5. Set-up: by 14:00 on Monday, June 2 Dismantling: from 12:00 until 15:00 on Thursday, June 5

#### The location of posters will be indicated by ID number of the paper on boards

Fixing material (Tape etc.) will be available in the poster presentation venue. Posters not removed after the dismantling period will be discarded by the secretariat and will not be sent back to the author.

# **SOCIAL EVENTS**

#### **Monday Welcome Reception**

Date & Time: Monday, June 2, 18:00–20:30 Venue: Civic Hall, 2nd Floor of Kumamoto-Jo (Castle) Hall Admission:

Symposium participants: Included in registration fee Accompany person: Additional ticket required Dress Code: No specific dress code

#### Banquet

Date & Time: Wednesday, June 4, Door Open 18:30, Start 19:00 Venue: Banquet Hall "Aso", 5th Floor, Hotel Nikko Kumamoto Admission:

Symposium participants: Included in registration fee (Not included in student registration)

Accompany person: Additional ticket required

Dress Code: No specific dress code

#### LUNCH

During the conference: Lunch time Venue: Civic Hall, 2nd Floor of Kumamoto-Jo (Castle) Hall Admission: Symposium participants

# AWARDS

#### ISPSD 2024 OHMI BEST PAPER AWARD

#### Development of Vertical-Channel Fin-SiC MOSFET for 3.3 kV applications

Tomoka Suematsu<sup>1,2</sup>, Takeru Suto<sup>1</sup>, Yuki Mori<sup>1</sup>, Haruka Shimizu<sup>1</sup>, Yasunori Tanaka<sup>2</sup> and Akio Shima<sup>1</sup>

<sup>1</sup>Research and Development Group, Hitachi, Ltd., Kokubunji, Tokyo, Japan <sup>2</sup>National Institute of Advanced Industrial Science and Technology, Tsukuba, Ibaraki, Japan

#### Abstract:

We have developed a 3.3 kV SiC Vertical-Channel Fin MOSFET, original structure named VC Fin-SiC. VC Fin-SiC features a fin-shaped channel and a JFET region arranged perpendicularly beneath the fin, allowing for increased designability and scalability. This structure increases the number of JFETs and channels per active area while protecting trench corners with a P-region. The JFET structure was optimized using TCAD simulation to achieve low on-resistance and high reliability. Evaluation of static and switching properties demonstrated that VC Fin-SiC can achieve a 30% reduction in on-resistance while maintaining a high threshold voltage, and a 30% reduction in switching loss due to fast turn-on compared to DMOS. Through this research, we discovered the significance of designing the channel and JFET regions, even at high voltages where drift layer resistance is typically dominant.

**Tomoka Suematsu** received the B.S. degree from Hiroshima University in 2017 and the M.S. degree from Kyoto University in 2019. Since 2019, she has been working as a researcher at Hitachi, Ltd., and since 2021, also working at the National Institute of Advanced Industrial Science and Technology (AIST). Her research focuses on developing SiC power semiconductor devices and power electronics.

**Takeru Suto** received the B.E. degree in 2015 and the M.E. degree in 2017 from Tokyo Institute of Technology (now known as the Institute of Science Tokyo). He has been working as a researcher with the R&D group at Hitachi, Ltd. since 2017. His research interests include silicon carbide power semiconductor devices, device modeling, machine learning techniques, and diamond crystal growth for quantum devices.

**Yuki Mori** received the B.S. and M.S. degrees in physics from Keio University in 1996 and 1998, respectively, and the Ph.D. degree from the University of Tokyo in 2014. In 1998, she joined the Central Research Laboratory, Hitachi, Ltd. From 1998 to 2009, she worked on VLSI device and process technology, especially in charge of the reliability analysis in dynamic random- access memories. Since 2010, she has been working on developing silicon carbide power devices. Her current research interests include the reliability of power devices.

**Haruka Shimizu** received the B. E. and M. E. degrees in material science from the University of Tokyo in 2003 and 2005 respectively, and received the Ph. D degree from Tsukuba University in 2020. In 2005, he joined the Central Research Laboratory at Hitachi, Ltd. His work has focused on advancing technologies related to SiC SBD, JFET, and MOSFET, contributing to the field of power semiconductor innovation.

**Yasunori Tanaka** received the Ph.D. degree in electronic engineering from Osaka University in 1996. In 1996, he joined the Quantum Radiation Division at Electrotechnical Laboratory. Since 2001, he has been working in the National Institute of Advanced Industrial Science and Technology conducting research on SiC power devices.

**Akio Shima** received the B. E. and M. E. degrees in applied physics from the University of Tokyo in 1993 and 1995 respectively, and received the Ph. D degree from Waseda University in 2008. He is now working as a Distinguished Researcher in Research & Development Group, Hitachi, Ltd., responsible for research activities on Energy Conversion Electronics including SiC power electronics and its industrial application.

#### ISPSD 2024 CHARITAT YOUNG RESEARCHER AWARD

# An Enhancement-mode AlGaN/GaN HEMT with Island-Ohmic p-GaN featuring stable threshold voltage and large gate swing

Xinyue Dai<sup>1,2</sup>, Qimeng Jiang<sup>1,2</sup>, Chao Feng<sup>3</sup>, Zhongchen Ji<sup>1,2</sup>, Sen Huang<sup>1,2</sup>, Runxian Xing<sup>4</sup>, Guohao Yu<sup>4</sup>, Xinguo Gao<sup>1</sup>, Xinhua Wang<sup>1,2</sup>, Xinyu Liu<sup>1,2</sup>

<sup>1</sup>Institute of Microelectronics of the Chinese Academy of Sciences, Beijing, China <sup>2</sup>University of Chinese Academy of Sciences, Beijing, China <sup>3</sup>Shenzhen Pinghu Laboratory, Shenzhen, China <sup>4</sup>Suzhou Institute of Nano-Tech and Nano-Bionics, Suzhou, China

#### Abstract:

A novel AlGaN/GaN HEMT based on an Island-Ohmic *p*-GaN gate (IO-PGaN) structure is proposed. Thanks to the Island-Ohmic, the "floating" *p*-GaN is connected with the gate terminal via the heavily doped  $p^{++}$ -GaN island. Therefore, the net charges generated in the *p*-GaN region under the gate or drain stress conditions, could be easily compensated by supplying holes via the ohmic gate structure, resulting in a stable threshold voltage ( $V_{TH}$ ). Meanwhile, a SiO<sub>2</sub> side wall is intentionally formed to achieve a moderate *E*-field at the island corner, and a JFET-like structure formed by the Schottky-metal/*p*-GaN junction delivers a self-limited gate leakage.

**Xinyue Dai** obtained the Ph.D. degree from the University of Chinese Academy of Sciences (Institute of Microelectronics, CAS) in 2024, where her research focused on the fabrication and optimization design of p-GaN power devices. Currently, she is working at Shenzhen Pinghu Laboratory as an Assistant Researcher. Her current research interests include the modeling and optimization of GaN HEMTs and related device technologies..

#### ISPSD 2024 BEST POSTER AWARD

#### 1-kV β-Ga<sub>2</sub>O<sub>3</sub> UMOSFET with Quasi-Inversion Nitrogen-Ion-Implanted Channel

Qi Liu<sup>1</sup>, Xuanze Zhou<sup>1</sup>, Man Hoi Wong<sup>2</sup>, Huidong Yao<sup>1</sup>, Jingbo Zhou<sup>1</sup>, Xiaodong Zhang<sup>3</sup>, Guangwei Xu<sup>1</sup>, Shibing Long<sup>1</sup>

<sup>1</sup>School of Microelectronics, University of Science and Technology of China, Hefei, China <sup>2</sup>Department of Electronic and Computer Engineering, Hong Kong University of Science and Technology, Hong Kong, China

<sup>3</sup>Suzhou Institute of Nano-Tech and Nano-Bionics, Chinese Academy of Sciences, Suzhou, China

#### Abstract:

We demonstrated 1-kV vertical enhancement-mode  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> U-shaped trench gate metal-oxide-semiconductor field-effect transistors (UMOSFETs) with nitrogen-ion-implanted channel. The nitrogen-ion-implanted region serves as a current blocking layer (CBL) and also allows a quasi-inversion channel to form at the trench sidewall. The activation annealing temperature of the nitrogen-ion-implanted CBL was optimized to suppress the leakage current. The CBL annealed at higher temperature exhibits better current blocking capability than its counterpart annealed at lower temperature. Based on the CBL annealed at higher temperature, the UMOSFET exhibits an improved on-off ratio of ~10<sup>6</sup>, an on-resistance of 87.6 m  $\Omega \cdot cm^2$  and a remarkable breakdown voltage of 1028 V. This is the first 1-kV  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET based on CBL, showing the potential of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> UMOSFETs with nitrogen-ion-implanted channel for kilovolt-class applications.

**Qi Liu** received the B.E. degree from Jiangnan University, Wuxi, China in 2020. She is currently pursuing the Ph.D. degree with the School of Microelectronics, the University of Science and Technology of China (USTC), Hefei, China. Her research mainly focuses on the design, optimization and characterization of gallium oxide power transistors.

**Xuanze Zhou** received his PhD from the University of Science and Technology of China (USTC) in 2023 and continued as a postdoctoral researcher at the same institution. Since 2018, his research has centered on gallium oxide-based power MOSFETs. Following his graduation, his interests expanded to include gallium oxide materials, defect characterization, MOCVD growth, and power MOSFET development.

**Man Hoi Wong** received the B.S. degree from Cornell University in 2004 and his Ph.D. degree from the University of California Santa Barbara in 2009. From 2013 to 2019, he developed  $Ga_2O_3$  power devices at Japan's National Institute of Information and Communications Technology. Currently, he is an associate professor of Electronic and Computer Engineering at the Hong Kong University of Science and Technology, where he engages in fundamental and applied research of ultrawide-bandgap semiconductors such as  $Ga_2O_3$ .

**Huidong Yao** received the B.S. degree from Nanjing University of Science and Technology, Nanjing, China in 2022. She is currently pursuing the Ph.D. degree with the School of Microelectronics, the University of Science and Technology of China, Hefei, China. Her research mainly focuses on the design, fabrication, and characterization of current blocking layers in gallium oxide for high-power electron devices.

**Jingbo Zhou** received the B. S. degree from University of Science and Technology of China, China, in 2023. Currently, he is a doctoral student studying characterizations of compensation doping for power devices on gallium oxide at University of Science and Technology of China and a visiting student at Sorbonne University. He is also working on establishing an analytical model of gallium oxide power transistors through electrical and magnetic properties.

**Xiaodong Zhang** received the Ph.D. degree from the University of Science and Technology of China, Hefei, China, in 2022. He is currently a Professor with the Suzhou Institute of Nano-Tech and Nano-Bionics (SINANO), Chinese Academy of Sciences (CAS), Suzhou, China. His main research interests include the epitaxial growth of ultrawide bandgap semiconductor gallium oxide and Aluminum Nitride films, power and optoelectronic devices, etc.

**Guangwei Xu** received his PhD from the Institute of Microelectronics of the Chinese Academy of Sciences in 2017. Then, he joined the University of California, Los Angeles as a postdoc. He joined the University of Science and Technology of China as a research fellow in the Shibing Long Group in 2019. His research focuses on wide bandgap semiconductor power device fabrication, device defect state measurement and device modeling.

**Shibing Long** is a full professor at the School of Microelectronics, University of Science and Technology of China. He received his PhD from the Institute of Microelectronics of the Chinese Academy of Sciences in 2005. Then, he worked there from 2005 to 2018 and joined the University of Science and Technology of China in 2018. His research focuses on micro- and nanofabrication, RRAM, ultrawide bandgap semiconductor devices (power devices and detectors) and memory circuit design.

#### **ISPSD HALL OF FAME**

**Michael S. Adler** for his contributions to modern power semiconductor technology, and his leadership role in organizing ISPSD conferences

**Gehan Anil Joseph Amaratunga** for his contributions to modern power semiconductor technology, and his leadership role in organizing ISPSD conferences

**B. Jayant Baliga** for his contributions to modern power semiconductor technology, and his leadership role in organizing ISPSD conferences

Xingbi Chen\* for his contributions to superjunction power semiconductor devices

**Tat-Sing Paul Chow** for his contributions to silicon and wide bandgap power semiconductor devices, and his leadership role in organizing ISPSD conferences

**Claudio Contiero** for his contributions to the proliferation of BCD technologies, and to the ISPSD conferences

**Mohamed Darwish** for his contributions to the advancement of power semiconductor technology, and his leadership role in organizing ISPSD conferences

**Don Disney** for contributions to power IC technology, and his leadership role in organizing ISPSD conferences

Taylor R. Efland for his contributions to power IC technology, and his leadership role in organizing ISPSD conferences

**Wolfgang Fichtner** for his contributions to MOS gated thyristors and TCAD modeling tools, and his leadership role in organizing ISPSD conferences

**Tatsuhiko Fujihira** for his contributions to superjunction power semiconductor technologies and industrialization of power semiconductor devices

Min-Koo Han for his contributions to modern power semiconductor technology, and his leadership role in organizing ISPSD conferences

**Oliver Häberlen** for his contributions to trench MOSFET and power GaN technology, and for his outstanding leadership in organizing ISPSD 2020 during the pandemic

Phil Hower for his contributions to power device safe operating area study and power IC technology

André A. Jaecklin for his contributions to modern power semiconductor technology, and his leadership role in organizing ISPSD conferences

**Daniel Kinzer** for his contributions to power MOSFET technology, and his leadership role in organizing ISPSD conferences

Thomas Laska for his contributions to IGBT technology and devices

Alex Lidow for contributions to silicon and GaN power device technology

**Leo Lorenz** for his contributions to modern power semiconductor technology, and his leadership role in organizing ISPSD conferences

**Gourab Majumdar** for his contributions to IGBT and intelligent power module technology, and his leadership role in organizing ISPSD conferences

Hiroyuki Matsunami for his contributions to the developments of silicon carbide epitaxial technology and wide bandgap power semiconductor devices

José Millán\* for his contributions to modern power semiconductor technology, and his leadership role in organizing ISPSD conferences

**Peter Moens** for his contributions to integrated power technology and GaN power device and reliability, and his leadership role in organizing ISPSD conferences

**Mutsuhiro Mori** for his contributions to high voltage insulated gate bipolar transistor for traction and high voltage systems, and his leadership role in organizing ISPSD conferences

Akio Nakagawa for his contributions to IGBT and power IC technology

Hiromichi Ohashi for his contributions to modern power semiconductor technology, and his leadership role in organizing ISPSD conferences

Tadahiro Ohmi\* for his contributions to modern power semiconductor technology, and his leadership role in organizing ISPSD conferences

Masahiro Okamura for his contributions to modern power semiconductor technology, and his leadership role in organizing ISPSD conferences

John Palmour\* for his contributions to SiC technology and devices

James Plummer for his contributions to MOS-bipolar power devices and power ICs, and for inspiring and training a new generation of device researchers

**C. Andre T. Salama** for his contributions to power IC technology, and his leadership role in organizing ISPSD conferences

Yasukazu Seki for his contributions to IGBT technology, and his leadership role in organizing ISPSD conferences

John Shen for contributions to high-frequency power MOSFET and leadership role in organizing ISPSD

**Kuang Sheng** for his contributions to SiC power device technology, and his leadership role in organizing ISPSD conferences

**M. Ayman Shibib** for his contributions to modern power semiconductor technology, and his leadership role in organizing ISPSD conferences

**Dieter Silber** for his contributions to modern power semiconductor technology, and his leadership role in organizing ISPSD conferences

Johnny Sin for his contributions to the design and commercialization of power semiconductor devices and his leadership role in organizing ISPSD conferences

Jan Šonský for his contributions to GaN device technology, and his leadership role in organizing ISPSD conferences

**Paolo Spirito** for his contributions to modern power semiconductor technology, and his leadership role in organizing ISPSD conferences

Yoshitaka Sugawara for his contributions to modern power semiconductor technology, and his leadership role in organizing ISPSD conferences

**Yoshiyuki Uchida** for his contributions to modern power semiconductor technology, and his leadership role in organizing ISPSD conferences

Florin Udrea for inspiring a generation of engineers to excel in power semiconductors and his numerous contributions to the field and to ISPSD

Daisuke Ueda for his work on trench structure MOS devices and GaN devices

Harry Vaes for his contributions to RESURF technology

Jan Vobecký for pushing the limits of diodes and thyristors by carrier lifetime engineering

Carl Frank Wheatley\* for his contributions to IGBT and radiation-hard power device technology

**Richard K. Williams** for his contributions to trench power MOSFET and power IC technology, and his leadership role in organizing ISPSD conferences

Toshiaki Yachi for his contributions to modern power semiconductor technology, and his leadership role in organizing ISPSD conferences

\*Deceased member

#### **PLENARY TALKS**

Main Hall (4th Floor) Date: June 2 (Monday) 9:00-10:20

#### Gallium Nitride; Past, Present and Future in an Ever-Changing Market Prof. Umesh Mishra, ECE Department, UC Santa Barbara, CA, USA

Gallium Nitride is a very exciting solution for many power electronics applications as the market continues to evolve and, in many ways, may emerge as even more important than Si and SiC. The primary reason remains its superior materials properties, most importantly the high mobility that is afforded by the AlGaN/GaN heterojunction. Lateral GaN power devices are attractive because the full region that holds voltage is a high electron mobility region and it is uniquely capable of delivering bidirectional voltage blocking, important in many applications including, solar inverters, chargers and motor drives. Lateral devices are also amenable to integrating smart functionality with the device. The drawback of a lateral device is a larger chip size and the need for field plates to manage fields, issues that can be mitigated with superjunction technology, now being investigated by multiple research institutions. Vertical GaN devices, on the other hand, are attractive for small chip-size and high-voltage rating, but have significantly lower electron mobility and require low dislocation density bulk substrates for reliable operation, which can increase cost. In this talk we will go over the history of GaN device evolution for power electronics applications and make predictions for the future.

#### Chuo Shinkansen with Superconducting Maglev and Semiconductor Power Conversion

#### Mr. Junichi Kitano, Central Japan Railway Company, Japan

The Chuo Shinkansen is a high-speed mass transport system that will connect Tokyo, Nagoya and Osaka in about one hour at a speed of 500 km per hour. Construction is currently underway between Shinagawa and Nagoya as a successor to the Tokaido Shinkansen.

The superconducting maglev levitates 10cm without control due to the dynamic electromagnetic induction between the superconducting magnets mounted on the vehicle and the levitation and guidance coils on the ground, and travels at ultra-high speeds of 500km/h inside a U-shaped concrete guideway. The key to the levitation and travel of the superconducting maglev is the strong magnetic force of the superconducting magnets and linear motor technology. The superconducting magnets are used in common with the field magnets of the linear synchronous motors, and each side of the vehicle constitutes a different motor.

The 16-car train has a capacity of approximately 1,000 passengers and is a large-capacity transportation system that can run more than eight trains per hour. Compared to general railways that use steel wheels and run on rails, there is no restriction of friction (adhesion) between wheel and rail, which allows for ultra-high speeds and high acceleration and deceleration, so there is a high utilization rate of the vehicles and the advantage that mass transportation can be achieved with a small number of trains.

Ten mainline substations will be installed between Shinagawa and Nagoya. Each substation will have six 60MVA inverters on double tracks, and installation of converters is already underway at some substations.

Thus, semiconductor power conversion is a key technology for superconducting maglev, and since the emergence of large-capacity thyristors, it has grown together with new semiconductor power devices such as light-triggered thyristors, GTOs, IGBTs, GCTs, and IEGTs.

Also, Dynamic WPT is used to supply around 1MW of auxiliary power to vehicles that levitate without contact, and here too high-frequency semiconductor power conversion technology is important. The advent of SiC semiconductors has made it possible to build efficient systems.

Innovative superconducting maglev technology is not unique to Japan. We hope that this new transportation system, which will connect Tokyo and Osaka in just one hour, will bring new possibilities to the world.

#### **SHORT COURSE**

Venue: Civic Hall (2nd Floor) Date: June 1 (Sunday) 8:30-16:30

Short Course Chair: Dr. Tatsuya Nishiwaki, Toshiba Electronic Devices & Storage, Japan

# SC1: 200mm SiC Substrate development and 300mm SiC opportunities & challenges

Dr. Chao Gao, SICC, China

**Abstract:** Technical development of large-sized SiC substrates will be presented in the meeting. Progress of 200 mm SiC substrate in volume production as well as the technical focus from both material and device side will be elaborated.

Besides, 300 mm SiC substrates is developed and the progress will be presented. The challenges and opportunities of 300 mm in the industry is to be discussed.

#### SC2: Technology for p-GaN gate High-voltage Gallium Nitride Transistors

#### Mr. Yasuhiro Uemoto, Infineon Technologies, Japan

**Abstract:** GaN power devices are basically normally on devices that take advantage of the superior material properties of 2DEG and high mobility due to the AlGaN/GaN heterostructure. This is a great gift from the nature. However, in actual use, normally off devices are strongly desired, and as a result of the challenges by many researchers, normally off structures with p-GaN gate become the mainstream in the market. In recent years, GaN has encountered chargers in the consumer market as a killer application, and the market has begun to expand. However, in the near future, in addition to the consumer market, there is no doubt that markets requiring more reliable devices, such as industrial and automotive, will expand drastically. This session will go back to the basics to explain the benefits and technologies of GaN power devices. E-mode GaN and d-mode GaN technologies will be outlined as well as a comparison of p-GaN gates in GIT and Schottky structures. In addition, Dyn Rdson behavior related to C in GaN buffers will be presented.

# SC3: Overview of Silicon Power Devices: History, Trends and Outlook

#### Prof. Wataru Saito, Kyushu University, Japan

**Abstract:** The power device market has been steadily expanding toward carbon neutrality, and continuous growth is expected in the future. While wide-bandgap semiconductor power devices, such as SiC and GaN, have been commercialized and are experiencing rapid market growth, they have yet to surpass silicon power devices in market share. Even in 2030, silicon power devices are projected to account for more than 80% of the market.

In this lecture, an overview of silicon power devices, covering their history, trends, and future outlook, is provided. One key aspect of power electronics development is the increasing power density of systems. Power device performance improvements have significantly contributed to this trend, and the evolution of device structures and advancements in process technologies that have driven these improvements are discussed. Additionally, recent R&D efforts aimed at further enhancing performance, as well as the transition to larger wafer diameters of 300 mm to expand production capacity, are introduced.

#### SC4: Recent Requirements and Trends on Power IC Technology Dr. Sang Gi Lee, DB HiTek, South Korea

**Abstract:** The power IC market is projected to grow from 2025 to 2028 at a CAGR of 4.1% (Omdia, 2025). As the market expands and product diversity increases, the requirement for the device and process option supported by BCD (Bipolar-CMOS-DMOS) technology is becoming more critical, not only for maintaining cost-competitiveness but also for enhancing functionality. Therefore, competition is intensifying around differentiated device

performance, value-added process options, and design-friendly PDK features.

This presentation will discuss power device performance, figures of merit, challenges in process integration, and the new PDK capabilities required by recent BCD technology. First, we will explore the performance requirements of LDMOS, a core component of Power ICs, across different applications, strategies for achieving target performance, key reliability aspects, and evaluations of large-size LDMOS devices comparable to discrete components. Next, we will discuss isolation schemes and special process options, such as HV capacitor, galvanic isolation, and embedded ReRAM. Finally, we will briefly cover the latest PDK features in modeling, ESD solutions, and P-cell.

#### SC5: Power Electronics Design Automation Tools: Steps towards Realization

#### Dr. Tristan Evans, PE-Systems, Germany

**Abstract:** The methods employed in designing power systems must be reconsidered as new semiconductor devices and technologies continue to proliferate. Modern design engineers are faced with an accelerating growth in power electronics applications, yet their ranks do not scale at the same rate. Compounding this, the traditional design flow for components and converters follows highly iterative, manual, intensive, and time-consuming cycles. The neighboring field of VLSI solved many of these problems by developing electronic design automation (EDA) tools in the 80s. This short course will explore ways in which EDA tools for power electronics are beginning to introduce new design flows—exploring more possibilities in shorter time. Also addressed will be ways to improve quality and quantity of component data and better ways to distribute it among trusted partners so that machine learning and Al-driven design techniques can be fully realized.

#### SC6: Al-assisted Reliability Testing, Modeling, and Condition Monitoring for Power Semiconductor Modules

#### Prof. Huai Wang, Aalborg University, Denmark

**Abstract:** With an increasing percentage of electricity being processed by power electronic converters, optimizing efficiency and reliability is critical for affordable, secure, and sustainable energy systems. Power semiconductor modules have been widely used for power electronic converters. Therefore, its reliability performance, both qualitative and quantitative aspects, is of critical important. Artificial Intelligence (AI) is increasingly solving optimization, regression, and classification problems within the energy sector, where deep electrification and digitalization intersect. This short course focuses on the application of AI in the reliability aspect study of semiconductor modules for power electronics, including AI-assisted reliability testing for testing time reduction, fast dynamic thermal modeling, and condition monitoring for predictive maintenance. A few case studies will be introduced to demonstrate how AI can assist in addressing the challenges in power semiconductor module reliability research.

#### SC7: Chip Embedded Power Package Technologies for Al and Vehicles Mr. Yoshiaki Aizawa, AOI ELECTRONICS, Japan

**Abstract:** In the field of semiconductor power packaging, wiring resistance and inductance have become a major concern for increasing power and switching frequency. Especially in Al/Data Center and EV applications, package inductance has a critical impact on power integrity, switching noise generation and switching uniformity. This power integrity also affects signal integrity and ultimately degrades processor chip performance in Al/Data Center application. Chip-embedded packages have attracted much attention in recent years as a promising solution to these issues. This course will introduce the development history, technical features, and development roadmap of the chip-embedded power package, in particular the panel-level package for Al/Data Center and EV.

#### **TECHNICAL PROGRAM**

#### **MONDAY, JUNE 2, 2025**

#### 8:30 - 9:00 4F Main Hall Opening Session

#### **Opening Remarks**

Ichiro Omura, General Chair Kyushu Institute of Technology, Japan

#### ISPSD 2024 Ohmi Best Paper Award

Nando Kaminski, General Chair of ISPSD 2024 University of Bremen, Germany Ulrike Grossner, Technical Program Committee Chair of ISPSD 2024 ETH Zurich, Switzerland

#### **Program Introduction**

Yuichi Onozawa, Technical Program Committee Chair Fuji Electric, Japan

#### 9:00 - 10:20 4F Main Hall Plenary Session

Chairs: Ichiro Omura (Kyushu Institute of Technology, Japan) David Sheridan (Alpha & Omega Semiconductor, USA)

- 9:00 9:40 Gallium Nitride: Past, Present and Future in an Ever-Changing Market Umesh Mishra ECE Department, UC Santa Barbara, CA, USA

- 9:40 10:20 Chuo Shinkansen with Superconducting Maglev and Semiconductor Power Conversion

Junichi Kitano Central Japan Railway Company, Tokyo, Japan

#### 10:20 - 10:50 3F A1/A2 Room and Foyer (Exhibition Area) Coffee Break

#### 10:50 - 12:30 4F Main Hall

#### HV-1: New Power Device Designs and Gate Control Method

**Chairs:** Wentao Yang (*HUAWEI Technologies, China*) Karthik Padmanabhan (*Alpha & Omega Semiconductor, USA*)

#### 10:50 - 11:10 Shallow Active Trench CSTBT<sup>™</sup> with Low Switching Loss for 6.5kV Class Kakeru Otsuka, Ayanori Gatto, Koji Tanaka, Shinya Soneda Power Device Works, Mitsubishi Electric, Fukuoka, Japan

# 11:10 - 11:30 Influence of IGBT Switching Behavior on Conducted and Radiated Emissions below 30 MHz

Yosuke Sakurai<sup>1</sup>, Yasutoshi Yoshioka<sup>2</sup>, Marco A. Azpúrua<sup>3</sup>, Jordi Solé-Lloveras<sup>3</sup>, Rik W. De Doncker<sup>4</sup>

<sup>1</sup>Semiconductors Business Group, Fuji Electric, Matsumoto, Japan; <sup>2</sup>Corporate R&D Headquarters, Fuji Electric, Tokyo, Japan; <sup>3</sup>EMC Electromagnetic BCN, S.L., Barcelona, Spain; <sup>4</sup>Institute for Power Electronics and Electrical Drives, RWTH Aachen University Aachen, Germany

# 11:30 - 11:50 First demonstration of 6.5kV fully scaled IGBT with ultra-shallow edge termination (USET)

Takuya Saraya<sup>1</sup>, Kiyoshi Takeuchi<sup>1</sup>, Kazuo Itou<sup>1</sup>, Toshihiko Takakura<sup>1</sup>, Munetoshi Fukui<sup>1</sup>, Shinichi Suzuki<sup>1</sup>, Hiroyuki Takase<sup>1</sup>, Wataru Saito<sup>2</sup>, Shin-Ichi Nishizawa<sup>2</sup>, Toshiro Hiramoto<sup>1</sup>

<sup>1</sup>*The University of Tokyo, Tokyo, Japan;* <sup>2</sup>*Kyushu University, Fukuoka, Japan*

# 11:50 - 12:10 A Novel 4.5 kV nonlatching IGCT for turn-on di/dt controllability without a clamp circuit

Gurunath Vishwamitra Yoganath<sup>1</sup>, Jan Fuhrmann<sup>1</sup>, Tobias Wikström<sup>2</sup>, Hans-Günter Eckel<sup>1</sup>

<sup>1</sup>Institute for Electrical Power Engineering, University of Rostock, Germany; <sup>2</sup>Hitachi Energy, Semiconductors, Switzerland

# 12:10 - 12:30 New Bidirectional Asymmetric High Voltage TVS (Transient Voltage Suppressor) device

Boris Rosensaft<sup>1</sup>, Xingchong Gu<sup>2</sup>, Martin Schulz<sup>3</sup>

<sup>1</sup>SBU Bipolar Chip R&D, IXYS Global Services GmbH, Lampertheim, Germany; <sup>2</sup>Pl&NPD Littelfuse Semiconductor, Wuxi, China; <sup>3</sup>Semiconductor Power Applications, Littelfuse Europe GmbH, Bremen, Germany

# 12:30 - 14:00 2F Civic Hall Lunch Break

Guangdong, China

# 14:00 - 15:40 4F Main Hall SiC-1: Performance of Superjunction SiC devices Chairs: Ulrike Grossner (*ETH Zurich, Switzerland*) Noriyuki Iwamuro (*University of Tsukuba, Japan*) 14:00 - 14:20 Avalanche and Short Circuit Withstand Capabilities in 3.3 kV-class SiC Superjunction MOSFET Shinichiro Matsunaga<sup>1</sup>, Takeshi Tawara<sup>2</sup>, Syunki Narita<sup>2</sup>, Masakazu Baba<sup>2</sup>, Kensuke Takenaka<sup>1</sup>, Tadao Morimoto<sup>1</sup>, Shinsuke Harada<sup>1</sup> <sup>'</sup>Advanced Power Electronics Research Center, AIST, Tsukuba, Japan; <sup>2</sup>Fuji Electric, Matsumoto, Japan

#### 14:20 - 14:40 **Bipolar characteristics of 3.3kV-class 4H-SiC Epi-refilled Super-Junction Diodes** Haoyuan Cheng<sup>1</sup>, Hengyu Wang<sup>1</sup>, Chi Zhang<sup>1</sup>, Jiangbin Wan<sup>1</sup>, QianQian Que<sup>1</sup>, Han Wang<sup>1</sup>, Haoyu Wang<sup>1</sup>, Ce Wang<sup>1</sup>, Jingrui Han<sup>2</sup>, Hungkit Ting<sup>2</sup>, Kuang Sheng<sup>1</sup> 'College of Electric Engineering, Zhejiang University, Hangzhou, China; <sup>2</sup>Tianyu Semiconductor,

21

14:40 - 15:00 Comparative Study on Charge-Imbalance Super Junction Termination for 3kV 4H-SiC Full-SJ and Semi-SJ Devices

> Chi Zhang<sup>1</sup>, Hengyu Wang<sup>1</sup>, Haoyuan Cheng<sup>1</sup>, Jiangbin Wan<sup>1</sup>, Han Wang<sup>1</sup>, Haoyu Wang<sup>1</sup>, Ce Wang<sup>1</sup>, Zijian Hu<sup>1</sup>, Jingrui Han<sup>2</sup>, Hungkit Ting<sup>2</sup>, Kuang Sheng<sup>1</sup> <sup>1</sup>College of Electrical Engineering, Zhejiang University, Hangzhou, China; <sup>2</sup>Tianyu Semiconductor, Guangdong, China

#### 15:00 - 15:20 Investigation of static and dynamic behavior of silicon carbide semi-superjunction structure in Schottky barrier diodes

Hiroshi Kono, Katsuhisa Tanaka, Tsutomu Kiyosawa, Kenya Sano Toshiba Electronic Devices & Storage, Hyogo, Japan

# 15:20 - 15:40 Comparative Study of Different Layouts for 1.7kV Charge-Balance-Assisted SiC MOSFETs

Yuhan Duan<sup>1,2</sup>, Botao Sun<sup>3</sup>, Yuanlan Zhang<sup>3</sup>, Pan Liu<sup>1,2</sup>, Guangyin Lei<sup>1</sup>, Min Li<sup>1</sup>, Qingchun Jon Zhang<sup>1</sup>

<sup>1</sup>Academy for Engineering and Technology, Fudan University, Shanghai, China; <sup>2</sup>Research Institute of Fudan University in Ningbo, Ningbo, China; <sup>3</sup>SiChain Semiconductors (Ningbo), Ningbo, China

#### 15:40 - 16:10 3F A1/A2 Room and Foyer (Exhibition Area) Coffee Break

#### 16:10 - 17:50 4F Main Hall GaN-1: Novel GaN Power Device and Technologies 1

**Chairs:** Tom Chun-Lin Tsai (*TSMC, Taiwan*) Akira Nakajima (*AIST, Japan*)

# 16:10 - 16:30 First Demonstration of Optically-Controlled 650 V Power GaN HEMT with Ultrafast Switching Speed

Xin Yang<sup>1</sup>, Liyang Jin<sup>2</sup>, Matthew Porter<sup>3</sup>, Hongchang Cui<sup>1</sup>, Zineng Yang<sup>1</sup>, Hehe Gong<sup>1</sup>, Han Wang<sup>1</sup>, Linbo Shao<sup>2</sup>, Yuhao Zhang<sup>1</sup>

<sup>1</sup>Department of Electrical and Electronic Engineering, The University of Hong Kong, Hong Kong, China; <sup>2</sup>Bradley Department of Electrical and Computer Engineering, Virginia Tech, Blacksburg, USA; <sup>3</sup>Center for Power Electronics Systems (CPES), Virginia Tech, Blacksburg, USA

# 16:30 - 16:50 First Demonstration of a Fully-Vertical GaN Power finFET with Direct Optical Triggering

Jung-Han Hsia<sup>1</sup>, Joshua Andrew Perozek<sup>1</sup>, Joseph Park<sup>2</sup>, Tomás Palacios<sup>1</sup>

<sup>1</sup>*Microsystems Technology Laboratories, Massachusetts Institute of Technology, Cambridge, MA, USA;* <sup>2</sup>*MIT Lincoln Laboratory, Lexington, MA, USA*

# 16:50 - 17:10Enhanced Photon-Generated Hole Spreading in p-GaN Gate Double-Channel<br/>HEMT for Suppression of Back-Gating Effect from Si Substrate

Zheng Wu, Tao Chen, Yat Hon Ng, Haochen Zhang, Zongjie Zhou, Yan Cheng, Hang Liao, Yutao Geng, Yumeng Huang, Kevin J. Chen

Dept. of Electronic and Computer Engineering, The Hong Kong University of Science and Technology, Hong Kong, China

17:10 - 17:30 Low *R*<sub>oN</sub>*Q*<sub>G</sub> 1.2 kV-Class Normally-Off GaN Gate Injection Transistor on GaN Substrate with Asymmetric Gate Structure

Hiroyuki Handa, Naohiro Tsurumi, Masao Kawaguchi, Masahiro Ogawa, Daisuke Shibata, Yoshio Okayama, Satoshi Tamura *Manufacturing Innovation Division, Panasonic Holdings, Osaka, Japan*

# 17:30 - 17:50 Beyond 650 V Dynamic Switching of High Voltage AlGaN/GaN/AIN HEMTs on monocrystalline AIN Substrates

Houssam Halhoul<sup>1</sup>, Mihaela Wolf<sup>1</sup>, Frank Brunner<sup>1</sup>, Sven Besendörfer<sup>2</sup>, Martin Damian Cuallo<sup>1</sup>, Steffen Breuer<sup>1</sup>, Gleb Lukin<sup>2</sup>, Andreas Lesnik<sup>2</sup>, Elke Meissner<sup>2</sup>, Oliver Hilt<sup>1</sup>

<sup>1</sup>Ferdinand-Braun-Institut (FBH), Berlin, Germany; <sup>2</sup>Fraunhofer Institute for Integrated Systems and Device Technology IISB, Erlangen, Germany

18:00 - 20:00 2F Civic Hall Welcome Reception

#### TUESDAY, JUNE 3, 2025

#### 8:40 - 10:20 4F Main Hall

#### LVT: Low Voltage Power Devices

Chairs: Atsushi Sakai (Renesas Electronics, Japan) Raffaella Roggero (STMicroelectronics, Italy)

#### 8:40 - 9:00 Current Sharing in Trench MOSFETs During Fast Switching Transients

Riccardo Tambone<sup>1,2</sup>, Alessandro Ferrara<sup>1</sup>, Filippo Magrini<sup>3</sup>, Raymond J.E. Hueting<sup>2</sup> <sup>1</sup>Infineon Technologies Austria AG, Villach, Austria; <sup>2</sup>University of Twente, Enschede, The Netherlands; <sup>3</sup>Infineon Technologies AG, Neubiberg, Germany

#### 9:00 - 9:20 **Polysilicon trench diode based on P-N junction**

Lia Masoero<sup>1</sup>, Rosalia Germana<sup>1</sup>, Adriano Novarese<sup>1</sup>, Alfio Scuderi<sup>2</sup>, Monica Petralia<sup>2</sup>, Alessandro Nodari<sup>1</sup>, Patrick Calenzo<sup>1</sup>

<sup>1</sup>Digital & Smart Power Techn. & Digital FE Manuf., VIPower R&D, STMicroelectronics, Rousset, France; <sup>2</sup>Analog & Power Front-End Manufacturing, STMicroelectronics, Catania, Italy

#### 9:20 - 9:40 Segmented Centroid and Stress-buffered P-body Taps for Stable Multi-finger Power CMOS

JungHyun Oh<sup>1,2</sup>, JungKyung Kim<sup>3</sup>, JaeHong Jeong<sup>3</sup>, Hoon Chang<sup>3</sup>, OhKyum Kwon<sup>3</sup>, SoYoung Kim<sup>4</sup>

<sup>1</sup>Department of Semiconductor and Display Engineering, Sungkyunkwan University, Suwon, Korea; <sup>2</sup>Samsung Institute of Technology, Samsung Electronics, Yongin, Korea; <sup>3</sup>Foundry Business, Samsung Electronics, Yongin, Korea; <sup>4</sup>Department of Semiconductor Systems Engineering, College of Information and Communication Engineering, Sungkyunkwan University, Suwon, Korea

# 9:40 - 10:00 Charge Field Modulation Mechanism and Its Experiments in SJ-Based SOI BCD process

Wentong Zhang<sup>1</sup>, Jiangnan Mu<sup>1</sup>, Teng Liu<sup>1</sup>, Nailong He<sup>2</sup>, Liqi An<sup>2</sup>, Jingchuan Zhao<sup>2</sup>, Sen Zhang<sup>2</sup>, Ping Li<sup>3</sup>, Rongyao Ma<sup>3</sup>, Yongqiang Cai<sup>4</sup>, Ming Qiao<sup>1</sup>, Zhaoji Li<sup>1</sup>, Bo Zhang<sup>1</sup>

<sup>1</sup>State Key Laboratory of Electronic, Thin Films and Integrated Devices, University of Electronic Science and Technology of China, Chengdu, China; <sup>2</sup>Technology Development Department, CSMC Technologies, Wuxi, China; <sup>3</sup>China Resources Microelectronics, Chongqing, China; <sup>4</sup>Beijing Normal University, Beijing, China

#### 10:00 - 10:20 High Performance Producible 90nm CFP LDMOS with a Secondary DPN-ISSG FP

Shaoxin Yu<sup>1</sup>, Rongsheng Chen<sup>1</sup>, Bo Wang<sup>2</sup>, Xiaolong Zhao<sup>2</sup>, Qishun Yao<sup>2</sup>, Yan Jin<sup>2</sup>

<sup>1</sup>School of Microelectronics, South China University of Technology, Guangzhou, China; <sup>2</sup>R&D department, Runpeng Semiconductor Technology, Shenzhen, China

#### 10:20 - 10:50 3F A1/A2 Room and Foyer (Exhibition Area) Coffee Break

# 10:50 - 12:30 4F Main Hall ICD: Power IC Design

**Chairs:** Jingshu Yu (*Intel, USA*) Wei-Jia Zhang (*Analog Device, USA*)

#### 10:50 - 11:10 A Monolithic GaN IC with Temperature Compensated Active Clamp Driver and Short Circuit Protection for Wide Power Supply Range

Yi Lu<sup>1</sup>, Xin Ming<sup>1,2,3</sup>, Yao Qin<sup>1</sup>, Lin-min Chen<sup>1</sup>, Chun-wang Zhuang<sup>1</sup>, Xin-ce Gong<sup>1</sup>, Wen-xi Lu<sup>1</sup>, Bo Zhang<sup>1</sup>

<sup>1</sup>State Key Laboratory of Electronic, Thin Films and Integrated Devices, UESTC, Chengdu, China; <sup>2</sup>Shenzhen Institute for Advanced Study, UESTC, Shenzhen, China; <sup>3</sup>Institute of Electronic and Information of UESTC in Guangdong, Dongguan, China

#### 11:10 - 11:30 **Dynamic Reliability of IC-Interface GaN HEMTs Demonstrated under Ultra-Fast** (ns), High-Frequency (MHz) Gate Overvoltage Stress (>30 V)

Bixuan Wang<sup>1</sup>, Qihao Song<sup>1</sup>, Kalparupa Mukherjee<sup>2</sup>, Loizos Efthymiou<sup>2</sup>, Daniel Popa<sup>2</sup>, Giorgia Longobardi<sup>2</sup>, Dong Dong<sup>1</sup>, Florin Udrea<sup>2</sup>, Yuhao Zhang<sup>3</sup>

<sup>1</sup>Center for Power Electronics Systems (CPES), Virginia Tech, Blacksburg, USA; <sup>2</sup>Cambridge GaN Devices, Cambridge, UK; <sup>3</sup>Department of Electrical & Electronic Engineering, The University of Hong Kong, Hong Kong, China

#### 11:30 - 11:50 **12-V Tolerant Power-Rail ESD Clamp Circuit for Monolithic GaN-on-Silicon** Integrated Circuits

Chao-Yang Ke, Ming-Dou Ker

Institute of Electronics, National Yang Ming Chiao Tung University, Hsinchu, Taiwan

# 11:50 - 12:10 A Self-Powered Gate Driving Scheme Enabled by the GaN/SiC Cascode Power Device

Ji Shu<sup>1</sup>, Jiahui Sun<sup>1,2</sup>, Mian Tao<sup>3</sup>, Shi-Wei Ricky Lee<sup>3</sup>, Kevin J. Chen<sup>1</sup>

<sup>1</sup>Department of Electronic and Computer Engineering, The Hong Kong University of Science and Technology, Hong Kong, China; <sup>2</sup>College of Electrical Engineering, Zhejiang University, Hangzhou, China; <sup>3</sup>EPACK Lab, The Hong Kong University of Science and Technology, Hong Kong, China

#### 12:10 - 12:30 Closed-Loop Active Gate Driver IC With Gate Current Control When Collector Current Equals Load Current

Yaogan Liang, Yohei Sukita, Michihiro Ide, Makoto Takamiya The University of Tokyo, Tokyo, Japan

#### 12:30 - 14:00 2F Civic Hall Lunch Break

#### 14:00 - 15:20 4F Main Hall GaN-2: GaN Power Device Reliability and Tests

Chairs: Oliver Hilt (FBH, Berlin, Germany) Roy K.-Y. Wong (National Tsing Hua University, Taiwan)

#### 14:00 - 14:20 **Dynamic Stability and Reliability of Multi-Kilovolt GaN Monolithic Bidirectional HEMT**

Yuan Qin<sup>1</sup>, Yijin Guo<sup>1</sup>, Matthew Porter<sup>1</sup>, Ming Xiao<sup>3</sup>, Hehe Gong<sup>1</sup>, Zineng Yang<sup>1</sup>, Daniel Popa<sup>4</sup>, Loizos Efthymiou<sup>4</sup>, Kai Cheng<sup>5</sup>, Zhiqin Chu<sup>2</sup>, Han Wang<sup>2</sup>, Florin Udrea<sup>4,6</sup>, Yuhao Zhang<sup>2</sup>

<sup>1</sup>Center for Power Electronics Systems, Virginia Tech, Blacksburg, VA, USA; <sup>2</sup>Department of Electrical and Electronic Engineering, University of Hong Kong, Hong Kong, China; <sup>3</sup>Xidian University, Xi'an, China; <sup>4</sup>Cambridge GaN Devices, Cambridge, UK; <sup>5</sup>Enkris Semiconductor, Suzhou, China; <sup>6</sup>University of Cambridge, Cambridge, UK

#### 14:20 - 14:40 Verification of p-GaN Gate Lifetime Models through Wide Time-scale ( $\mu$ s- 10<sup>7</sup> s) Measurement

Sijiang Wu<sup>1</sup>, Siyuan Ye<sup>1</sup>, Jinjin Tang<sup>1</sup>, Junting Chen<sup>1</sup>, Shanshan Wang<sup>1</sup>, Junlei Zhao<sup>1</sup>, Zuoheng Jiang<sup>1</sup>, Haohao Chen<sup>1</sup>, Zheyang Zheng<sup>2</sup>, Jun Ma<sup>1</sup>, Mengyuan Hua<sup>1</sup>

<sup>1</sup>Department of Electronic and Electrical Engineering, Southern University of Science and Technology, Shenzhen, China; <sup>2</sup>School of Microelectronics, University of Science and Technology of China, Hefei, China

# 14:40 - 15:00 Ultrafast Junction Temperature Mapping During Surge Current Transient and Thermal Management in Vertical GaN PiN Diode

Jiahong Du<sup>1</sup>, Haobin Lin<sup>2</sup>, Dazhi Hou<sup>2</sup>, Shibing Long<sup>1</sup>, Shu Yang<sup>1</sup> <sup>1</sup>School of Microelectronics; <sup>2</sup>Department of Physics, University of Science and Technology of China, China

# 15:00 - 15:20 Mechanism of Leakage Current Degradation in p-GaN Gate HEMTs under Gamma Irradiation

Zhao Wang<sup>1</sup>, Qingchen Jiang<sup>1</sup>, Shenghuai Liu<sup>1</sup>, Xin Zhou<sup>1</sup>, Huan Gao<sup>1</sup>, Qi Zhou<sup>1</sup>, Zhao Qi<sup>1</sup>, Ming Qiao<sup>1,2</sup>, Bo Zhang<sup>1</sup>

<sup>1</sup>State Key Laboratory of Electronic, Thin Films and Integrated Devices, University of Electronic Science and Technology of China, Chengdu, China; <sup>2</sup>Shenzhen Institute for Advanced Study, University of Electronic Science and Technology of China, Shenzhen, China

#### 15:20 - 15:40 3F A1/A2 Room and Foyer (Exhibition Area) Coffee Break

#### 15:40 - 17:40 3F A3/A4 Room LVT-P: Low Voltage Power Devices 2 (Poster Session)

# A Novel Split Contact Field Plate LDMOS with a Floating Gate for Hot Carrier Degradation Improvement

Qiao Teng<sup>1</sup>, Yongyu Wu<sup>1,3</sup>, Kai Xu<sup>1,2</sup>, Dawei Gao<sup>1</sup>

<sup>1</sup>*College of Integrated Circuits, Zhejiang University, Hangzhou, China; <sup>2</sup>ZJU-Hangzhou Global Scientific and Technological Innovation Center, Zhejiang University, Hangzhou, China;* <sup>3</sup>*Zhejiang ICsprout Semiconductor, Hangzhou, China*

# Novel Optimization Method of Multi-Devices using TCAD Driven Machine Learning in BCD Process

Junhyeok Kim<sup>1</sup>, Kyuyeop Lee<sup>1</sup>, Yunjun Nam<sup>1</sup>, Joohyung Yoo<sup>1</sup>, Juwon Park<sup>2</sup>, Dawon Jeong<sup>1</sup>, Jaehyun Yoo<sup>1</sup>, Yonghee Park<sup>1</sup>, Dae Sin Kim<sup>1</sup>

<sup>1</sup>CSE team, Samsung Electronics, Hwasung-Si, Korea; <sup>2</sup>PA4 team, Samsung Electronics, Hwasung-Si, Korea

# Chip Layout Optimization of Trench Length and the Upper Electrode Contact in Trench Field Plate MOSFET

Casey Clendennen<sup>1</sup>, Tomoaki Shinoda<sup>1</sup>, Shinpei Onishi<sup>1</sup>, Hajime Kataoka<sup>1</sup>, Masaki Nagata<sup>2</sup>

<sup>1</sup>Device Development Dept., ROHM, Kyoto, Japan; <sup>2</sup>Global IT Infrastructure Dept., ROHM, Kyoto, Japan

# Irradiation Hardening of SGT Based on Combined IPO Structure and Mechanism Modeling of Leakage Current Optimization

Junyan Zhu<sup>1</sup>, Haonan Liu<sup>1</sup>, Jun Ye<sup>1,3</sup>, Xuan Xiao<sup>3,4</sup>, Ruihan Gao<sup>1</sup>, Junfeng Yu<sup>1</sup>, Xiaodong Yang<sup>1</sup>, Zhuang Wang<sup>1</sup>, Chunlei Wu<sup>1</sup>, Weiye Mo<sup>3</sup>, Hongping Ma<sup>5</sup>, Qingchun Zhang<sup>5</sup>, Liang Li<sup>6</sup>, Qingdong Zhang<sup>7</sup>, Tao Wang<sup>7</sup>, Wei Huang<sup>2</sup>, David Wei Zhang<sup>1</sup>

<sup>1</sup>Shanghai Institute of Intelligent Electronics & Systems, School of Microelectronics, Fudan University, Shanghai, China; <sup>2</sup>School of Integrated Circuits, Jiangnan University, Wuxi, China; <sup>3</sup>Wuxi China Resources Huajing Microelectronics, Wuxi, China; <sup>4</sup>College of Physics, Sichuan University, Chengdu, China; <sup>5</sup>School of Academy of Engineering & Technology, Fudan University, Shanghai, China; <sup>6</sup>School of Electronic Information Engineering, Suzhou Vocational University, Suzhou, China; <sup>7</sup>Wuxi Microelectronics Scientific and Research Center, Wuxi, China

# Integrated Fast-Recovery SGT-SBR Devices with Majority Carrier Modulation during Wide Temperature Range

Jun Ye<sup>1,2</sup>, Haonan Liu<sup>1</sup>, Ruihan Gao<sup>1</sup>, Xuan Xiao<sup>2,3</sup>, Junyan Zhu<sup>1</sup>, Weiye Mo<sup>2</sup>, Yang Song<sup>2</sup>, Xiaodong Yang<sup>1</sup>, Zhuang Wang<sup>1</sup>, Jiao Liang<sup>4</sup>, Hongping Ma<sup>4</sup>, Qingchun Zhang<sup>4</sup>, Wei Huang<sup>5</sup>, ChunLei Wu<sup>1</sup>, David Wei Zhang<sup>1</sup>

<sup>1</sup>State Key Laboratory of ASIC and System, Shanghai Institute of Intelligent Electronics & Systems, School of Microelectronics, Fudan University, Shanghai, China; <sup>2</sup>Wuxi China Resources Huajing Microelectronics, Wuxi, China; <sup>3</sup>College of Physics, Sichuan University, Chengdu, China; <sup>4</sup>Academy for Engineering & Technology, Fudan University, Shanghai, China; <sup>5</sup>School of Integrated Circuits, Jiangnan University, Wuxi, China

#### BCD HVpMOS with Double-Functional-RESURF to Improve HCI Reliability

Tomohiro Imai<sup>1</sup>, Atsushi Sakai<sup>1</sup>, Zen Inoue<sup>2</sup>

<sup>1</sup>*Process Tech and PDK Department, Operations Engineering Division, Renesas Electronics, Ibaraki, Japan;* <sup>2</sup>*MCU Device Technology Department, Device Technology Division, Renesas Electronics, Kumamoto, Japan*

# Novel Multistack Floating Field Plate MOSFET and Image Clustering-based Design Analysis

Hiro Gangi<sup>1</sup>, Yasunori Taguchi<sup>1</sup>, Kentaro Takagi<sup>1</sup>, Kouta Nakata<sup>1</sup>, Kairu Yoshida<sup>1</sup>, Taichi Fukuda<sup>1</sup>, Hiroki Nemoto<sup>1</sup>, Shotaro Baba<sup>1</sup>,Yusuke Kobayashi<sup>1</sup>, Tomoaki Inokuchi<sup>1</sup>, Tatsuya Nishiwaki<sup>2</sup>, Kenya Kobayashi<sup>2</sup>

<sup>1</sup>Corporate Research & Development Center, Toshiba, Kanagawa, Japan; <sup>2</sup>Advanced Semiconductor Device Development Center, Toshiba Electronic Devices & Storage, Kanagawa, Japan

#### Design and Performance Enhancement of Integrated Schottky Contact in Low-Voltage LDMOS on 55nm BCD Platform

Dingxiang Ma<sup>1</sup>, Yuanqing Ye<sup>2</sup>, Yangjie Liao<sup>1</sup>, Jiawei Wang<sup>1</sup>, Fanyi Zeng<sup>2</sup>, Bo Zhang<sup>1</sup>, Ming Qiao<sup>1,2</sup>

<sup>1</sup>State Key Laboratory of Electronic, Thin Films and Integrated Devices, University of Electronic Science and Technology of China, Chengdu, China; <sup>2</sup>Shenzhen Institute for Advanced Study, University of Electronic Science and Technology of China, Shenzhen, China

# High Reliability Tri-zone Heterogeneous Charge Balanced SJ-LDMOS with Novel Silicon Rich Oxide and Its Experimental Verification

Teng Liu<sup>1,2</sup>, Hao Wang<sup>2</sup>, Wentong Zhang<sup>1</sup>, Nailong He<sup>2</sup>, Shiyao Cai<sup>1</sup>, Yuxiao Kun<sup>1</sup>, Jiangnan Mu<sup>1</sup>, Zhekai Hu<sup>1</sup>, Ting Wang<sup>2</sup>, Ziao Zhang<sup>2</sup>, Liqi An<sup>2</sup>, Yongshun Li<sup>2</sup>, Huajun Jing<sup>2</sup>, Liang Song<sup>2</sup>, Sen Zhang<sup>2</sup>, Yongsheng Sun<sup>3</sup>, Hao Fang<sup>3</sup>, Sheng Dong Hu<sup>4</sup>, Ming Qiao<sup>1</sup>, Zhaoji Li<sup>1</sup>, Bo Zhang<sup>1</sup>

<sup>1</sup>State Key Laboratory of Electronic, Thin Films and Integrated Devices, University of Electronic Science and Technology of China, Chengdu, China; <sup>2</sup>Technology Development Department, CSMC Technologies, Wuxi, China; <sup>3</sup>Wuxi China Resources Microelectronics; <sup>4</sup>Chongqing University, Chongqing, China

#### 15:40 - 17:40 3F A3/A4 Room ICD-P: Power IC Design 2 (Poster Session)

# An On-Chip Tunable Negative Power Supply within SiC MOSFET Gate Driver for Spurious Conduction Suppression and Reliable Driving

Yun Dai, Zekun Zhou, Rongxing Lai, Zijun Zhou, Jiaxing Mao, Bo Zhang

*State Key Laboratory of Electronic Thin Films and Integrated Devices, University of Electronic Science and Technology of China, Chengdu, China*

# A Study on a 4H-SiC-Based ESD Protection Device with lower Operating Voltage Using an Additional PNP BJT Structure

U-Yeol Seo<sup>1</sup>, Jae-Yoon Oh<sup>1</sup>, Min-Seo Kim<sup>1</sup>, Dong-Hyun Kim<sup>1</sup>, Ji-Hye Yoo<sup>1</sup>, Hee-Bae Lee<sup>2</sup>, Seung-Hyun Kim<sup>2</sup>, Kyu-Hyun Jung<sup>2</sup>, Yong-Seo Koo<sup>3</sup>

<sup>1</sup>Dept. Engineering of Foundry, DanKook University, Yongin, Korea; <sup>2</sup>Tech Development Team3, DB HiTek, Bucheon, Korea; <sup>3</sup>Dept. Engineering of Electronics and Electrical, DanKook University, Yongin, Korea

### High Voltage Monolithic GaN Power IC with High Speed Low-power Consumption Level Shifter Circuit

Qianheng Dong<sup>1</sup>, Jing Zhu<sup>2</sup>, Yifei Zheng<sup>1</sup>, Haoran Wang<sup>1</sup>, Xiang Fan<sup>1</sup>, Zihang Chen<sup>1</sup>, Siyang Liu<sup>1</sup>, Weifeng Sun<sup>1</sup>, Kai Zhang<sup>3</sup>, Siyuan Yu<sup>4</sup>